講座概要

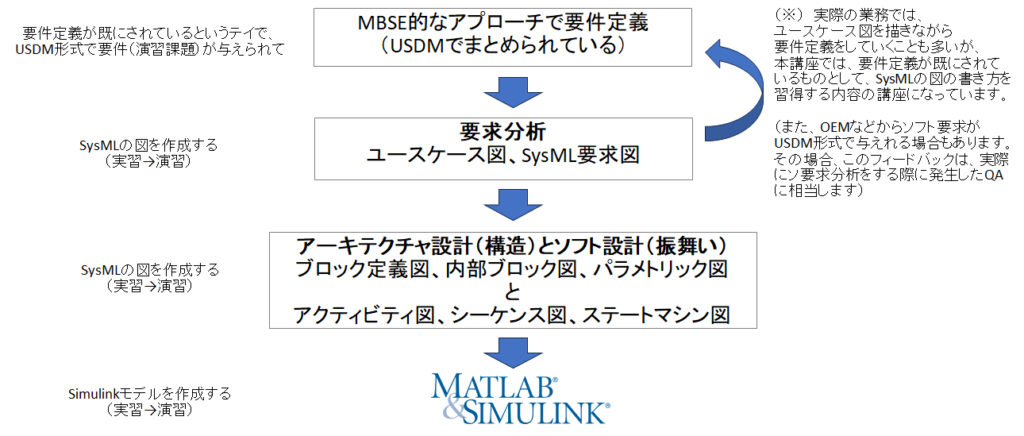

本講座は、ユースケース図、要求図、ブロック定義図、内部ブロック図、パラメトリック図、アクティビティ図、シーケンス図、ステートマシン図などのUML/SysMLの図が理解でき、それらの図の作成ができるエンジニアを育成する為の講座です。

本講座では、Enterprise Architectを使った演習→実習の繰り返しによって、これらの図の書き方を習得していきます。また、ツールの操作方法を習得することも可能です。

特徴

本講座の演習は、USDM形式で表現された要求(演習課題、実習課題)に対して、要求図などのSysMLの様々な図を作成する内容になっています。

そして、本講座の最大の特徴は、演習で作成した SysMLの図からMATLAB/Simulinkのモデルを作成 するという演習まで含まれている点です。これらの課題は、「CD-1 ボディ系システムのコントローラモデル作成講座」の課題と共通していますので、講座間の連携がとれた内容となっています。

対象者

- SysMLの図の理解(図の見方)が出来るようになりたい方

- SysMLの図が書けるようになりたい方

- SysMLの図(ソフトウェア設計)からSimulinkモデルが作成できるようになりたい方

予備知識

- 組込み開発などの製品開発の経験がある方(1年以上)

- Simulinkの基礎的な操作ができる方

対象バージョン/使用ツール

- SysML v1.5

- Enterprise Architect バージョン 17.1

Astah等の別のツールをお使いの方は、ご相談ください。

目次

| ■1日目 : SysMLにおける要求・構造設計の基礎 | |

| SysML基礎 | |

| ・はじめに(本講座の位置付けと目標) | |

| ・SysMLと発展の歴史 | |

| ・SysMLのダイアグラム体系 | |

| ・ツールの起動と基本操作(EA) | |

| 【演習】 EAの起動、プロジェクト作成 | |

| 【実習】 ルームランプ用EAプロジェクトの作成と保存 | |

| 要求定義 | |

| ・要求図の記法 | |

| 【演習】 USDMから要求図への変換方法 | |

| 【実習】 ルームランプ制御のUSDMを要求図に変換 | |

| ・要求の階層構造 | |

| 【演習】 Decomposition(分割)とDerive(派生)の使い分け | |

| 【実習】 上位要求から詳細要求への展開 | |

| ・ユースケース図の概念と記法 | |

| 【演習】 ユースケースによる要求の確認 | |

| 【実習】 ルームランプのユースケースを作成 | |

| 構造設計 | |

| ・ブロック定義図(BDD)とシステム境界 | |

| 【演習】 外部アクターとシステムの物理構成定義 | |

| 【実習】 システムの主要ブロック配置 | |

| ・ブロック間の関係定義 | |

| 【演習】 共有集約と合成集約 | |

| 【実習】 部品構成(ECU、センサ等)の定義 | |

| ■2日目 : SysMLにおける詳細構造とインターフェース設計 | |

| 内部構造 | |

| ・内部ブロック図(IBD)の基本と役割 | |

| 【演習】 BDDからIBDへのパーツ生成と配置 | |

| 【実習】 コントローラー内部の構成図作成 | |

| ・コネクタによる接続と通信経路 | |

| 【演習】 ネストされたパーツ間の接続手順 | |

| 【実習】 各パーツ間のコネクタ記述 | |

| ポート設計 | |

| ・プロキシポートとフルポートの概念 | |

| 【演習】 外部接続ポートの定義 | |

| 【実習】 ECUの入出力ポート定義 | |

| ・インターフェイスブロックの活用 | |

| 【演習】 複数の信号をまとめるポート設計 | |

| 【実習】 共通インターフェースの定義 | |

| 信号定義 | |

| ・フロープロパティと方向(in/out) | |

| 【演習】 信号の型(Boolean,Real等)の設定 | |

| 【実習】 ドア開閉信号のプロパティ定義 | |

| ・アイテムフローによる具体的な情報定義 | |

| 【演習】 コネクタ上を流れる情報の可視化 | |

| 【実習】 バス上を流れるデータの詳細定義 | |

| 内部構造まとめ | |

| ・多階層IBDの整合性 | |

| 【演習】 階層をまたぐポート接続 | |

| 【実習】 「ルームランプ」のIBD(完成) | |

| ■3日目 : SysMLにおける詳細設計(振る舞いと制約) | |

| 状態遷移 | |

| ・ステートマシン図:状態と遷移の基本 | |

| 【演習】 イベント、ガード条件、アクションの設定 | |

| 【実習】 ルームランプの点灯状態遷移 | |

| 相互作用 | |

| ・シーケンス図:時系列のメッセージ | |

| 【演習】 ライフライン間の通信タイミング | |

| 【実習】 ドア開閉から消灯までのシーケンス | |

| 処理フロー | |

| ・アクティビティ図:処理の順序 | |

| 【演習】 エッジ検出(立ち上がり) | |

| 【実習】 ボタン押下検出 | |

| ・オブジェクトフロー | |

| 【演習】 条件分岐と間と処理の構成 | |

| 【実習】 タイマー用カウンタロジックの作成 | |

| 制約 | |

| ・制約ブロックとパラメトリック図 | |

| 【演習】 数式の定義とパラメータ | |

| 【実習】 固定小数点変換の数式定義 | |

| ・パラメトリック結合 | |

| 【演習】 ブロック属性の数式の紐付け | |

| 【実習】 ヒステリシス判定 | |

| 振舞いモデルのまとめ | |

| ・振る舞いの割当 | |

| 【演習】 機能をハードウェアへ割り当てる | |

| 【実習】 作成したロジックのECUへの割り当て | |

| ■4日目 : SysMLモデルからSimulinkモデルの作成 | |

| SysMLモデルの検証 | |

| ・SysMLモデルでの検証の考え方(ヌケモレ、不整合) | |

| 【演習】 設計モデルの一貫性確認方法 | |

| 【実習】 ルームランプモデルの一貫性確認 | |

| Simulinkモデル作成の基礎 | |

| ・SysMLからSimulinkへのマッピング | |

| 【演習】 SysMLブロックをSimulink要素に変換 | |

| 【実習】 SysMLブロックをSimulinkサブシステムにマッピング | |

| 構造変換 | |

| ・IBDからSimulinkスケルトンの作成 | |

| 【演習】 ポートやバスをSimulink側で再現 | |

| 【実習】 ルームランプのSimulinkモデルを作成 | |

| 振舞い変換 | |

| ・ステートマシン図をStateflowに変換する | |

| 【演習】 タイマー処理のStateflow実装 | |

| 【実習】 ルームランプの点灯・消灯ロジックのStateflow実装 | |

| 総合演習 | |

| ・SysMLモデルからシミュレーションへ | |

| 【演習】 実装したSimulinkモデルの動作確認 | |

| 【実習】 要求を満たすかのシミュレーション検証 | |

| まとめ | |

| ・講座内容の振り返り | |

| ・SysML v2.0への展望と実務適用 | |

| ・質疑応答 |

日数

4日間(1日7時間)

受講料

オンサイト講座 1日:500,000円(税抜)

- 10名を越える場合は、受講料が変わってきますのでお問合せください。

- 本講座はSparx Systems社の「Enterprise Architect」、The Mathworks社の「MATLAB/Simulink」を使った演習となっています。別途、これらの各種ツールの使用料が必要になります。受講者様のお持ちのライセンスをご使用される場合など、事前にご相談ください。

- お客様のご要望に応じて、「1日の簡易版にしたい」、「SysMLではなく、UMLの講座にしたい」など、講座内容をカスタムすることも可能ですのでお気軽にご相談ください。また、EA以外の使用ツールで実施されたい場合についてもご相談ください。

- 遠方の場合の出張費など別途費用が発生する場合もございます。また、予告なく変更・改定になる場合がございますこと予めご了承ください。